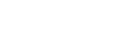

Aktuelle Echtzeit-Embedded-Systeme in Servo-Antrieben benötigen Hochleistungsarchitekturen, um feldorientierte Regelungsalgorithmen mit hohen Trägerfrequenzen implementieren zu können. Werden solche Systeme mit einer Positionsschleife und einer Pfadgenerierung kombiniert, nimmt die Rechenlast weiter zu. Bei Erweiterung des Systems um eine zweite Bewegungsachse steigt die Prozessor-Bandbreite ebenfalls.

Der Autor: Andreas Thamm, Renesas Electronics Europe, Düsseldorf

Viele aktuelle MCU-Lösungen bieten für diesen Anwendungsbereich nicht genug Prozessor-Bandbreite. Dieses Problem lässt sich über ein FPGA mit MCU oder ein FPGA mit einer Lösung auf Basis eines Soft-Cores abfedern. Dies erhöht jedoch Systemkosten und Komplexität. Eine weitere mögliche Lösung wäre die Nutzung einer MPU mit mehr Prozessor-Bandbreite. Die Herausforderung bei diesem Vorgehen ist, dass das Speichersystem mit höherem CPU-Takt nicht mehr mithalten kann, sodass entweder Wait-States oder ein High-Speed-Cache-Speicher zum Einsatz kommen muss. Cache-Speicher ist in einem harten Echtzeit-System problematisch, da ihm das nötige deterministische Verhalten für eine wohldefinierte Ausführungszeit fehlt. Eine typische Anwendung benötigt mehr Speicherplatz für Programme und Daten als der Cache bieten kann. Bei einem Cache-Miss müssen Code oder Daten aus dem langsameren Speicher geladen werden, was zu schwankenden Ausführungszeiten führt. Typische ARM-MPU-Cores haben zudem keinen vektorgesteuerten Interrupt-Controller, sodass die Software mehr Arbeitsschritte zum Finden der Interrupt-Quelle und zum Anstoßen der entsprechenden Interrupt-Service-Routine benötigt. Beim Auftreten mehrerer Interrupts führt die Kombination von Cachespeicher- und Interrupt-Controller ebenfalls zu nicht-deterministischem Verhalten und variierenden Ausführungszeiten.

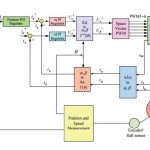

RZ/T1-Echtzeit-Prozessorkern

Zur Lösung dieses Problems hat Renesas den RZ/T1 unter Verwendung eines Cortex-R4F-Cores entwickelt. Der R4F-Core enthält einen ‚Nested Vector Interrupt Controller‘ sowie einen eng gekoppelten Speicher (Tightly Coupled Memory – TCM). Der Vektor-Interrupt-Controller adressiert den entsprechenden Interrupt-Handler direkt über die Vektortabelle mithilfe einer Hardware, die die Interrupt-Latenz auf ein Minimum senkt. Der TCM ist direkt und auf der gleichen Speicher-Hierarchiestufe wie der Cache-Speicher mit dem Core verschaltet. Der TCM ist ein einfacher SRAM ohne Tags ähnlich wie ein Cache-Speicher, der sich effizient implementieren lässt. Der ATCM umfasst 512 KByte und wird für Code genutzt. Der BTCM ist 32 kB groß und nimmt Daten auf. Durch die Nutzung von ATCM und BTCM können Entwickler Code und Daten voneinander trennen, sodass sie sich von der CPU gleichzeitig aufrufen lassen, ohne die Pipeline dazu anhalten zu müssen. Der RZ/T1 hat bis zu 1 MB zusätzlichen internen SRAM, auf den die CPU auf dem AXI-Bus über das L1-Cache-System zugreifen kann. Der L1-Cache ist organisiert als 8 kB für Code und 8 kB für Daten. Jeder Cache ist als physikalisch adressierter 4-fach assoziierender Cache aufgebaut. Die Cache-Zeilenlänge beträgt acht Worte. Der AXI-Bus ist auch mit einem externen Buscontroller verbunden, der SDRAM, NOR-Flash und seriellen NOR-Flash unterstützt.

Bei CPU-Taktgeschwindigkeiten unter 450 MHz arbeitet der ATCM mit Single-Cycle-Zugriff. Bei 450 oder 600 MHz umfasst die Zugriffszeit einen Wait-State. Dank 64-Bit-Oragisation, Pipelining und Branch-Flow-Vorhersage lässt sich der ATCM ohne Blockieren der Pipeline nutzen. Der Zugriff auf den BTCM erfolgt immer im Single-Cycle-Modus.

Jitter-Benchmark-Analyse

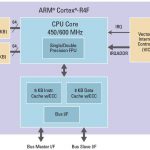

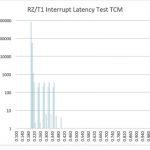

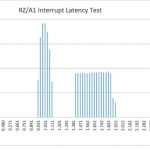

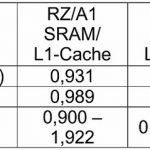

Zur Ermittlung der RZ/T1-Echtzeit-Leistung wurde ein Testcode erstellt. Dabei läuft der CoreMark-Benchmark als Hintergrund-Softwarelast, während in der Unterbrechungsroutine (ISR) Interrupt-Latenz und -Jitter gemessen werden. Der Prozessor lief bei einer Taktfrequenz von 600 MHz und der ATCM wurde für einen Wait-State mit aktivierter Branch-Flow-Vorhersage konfiguriert. Als Interrupt wurde ein Timer-Compare-Match verwendet, das einen Interrupt mit einer Wiederholrate von 40 kHz erzeugt und den Timer Counter zurücksetzt. Der Timer Counter wird in der ISR nach einem kompletten Context Switch ausgelesen, wobei alle Register abgespeichert werden. Die Anzahl an Ticks entspricht der Reaktionszeit zwischen dem Auftreten des IRQ-Events und dem des tatsächlichen Handler-Codes. Diese Daten wurden in einem Histogramm gespeichert und so lange zusammengefasst, bis der Benchmark 20.000 mal durchlaufen wurde. Die Messgranularität betrug 6,66 ns pro Timer-Tick. Dieser Test wurde zunächst mit Code und Daten im internen SRAM bei aktiviertem Cache als Basismessung durchgeführt. Dabei ergab sich eine Interrupt-Latenz von 200 ns und ein maximaler Jitter von 533 ns bei einer Probengröße von 821.077 Interrupts.

Anschließend wurde der Test unter Verwendung des TCMs wiederholt, wobei der Code im ATCM- und die Daten im BTCM-Speicher abgelegt waren. Die Ergebnisse zeigten eine Interrupt-Latenz von 200 ns und einen maximalen Jitter von 200 ns bei einer Probengröße von 882.098 Interrupts.

Zum Vergleich führte Renesas den gleichen Test auf einer RZ/A-MPU aus, die einen Cortex-A9-Prozessor mit einer Taktfrequenz von 400 MHz und einen großen internen SRAM enthält. Der Benchmark wurde im SRAM mit 32 kB L1-Instruction-Cache und 32 kB L1-Daten-Cache ausgeführt. Es kam kein L2-Cache zum Einsatz, da der interne SRAM (10 MB) auf der gleichen Specher-Hierarchie wie der L2-Cache angeordnet ist. Dabei ergaben sich eine Interrupt-Latenz von 900 ns sowie ein Jitter von 900 ns über 20.068 Interrupts. Dies zeigt, dass der RZ/A mit einer Rechenleistung von 1000 DMIPS beim Interrupt-Handling sogar langsamer ist als ein RZ/T mit 966 DMIPS.

Steuerungen mit deterministischem Verhalten

Arbeitet ein Servoantrieb beispielsweise bei 10 m/s und wird die Position mit einem Timing-Offset (ISR-Latenz + Jitter) von 1,922 µs erfasst, so kann dies zu einem Positionsfehler von 0,0192 mm führen. Beim RZ/T1 würde der Positionsfehler nur 0,004 mm betragen. Ein weiterer Jitter-Effekt zeigt sich in der PID-Schleife für die Geschwindigkeitssteuerung. Erfolgt die Positionsmessung mit Jitter, dann wird der Kd-Wert mit dem durch den Jitter im Messverlauf verursachten Fehler in der Encoder-Messung multipliziert. Dies kann zu Störungen bei der Geschwindigkeit führen, weil das System versucht, einen Fehler zu korrigieren, der eigentlich gar nicht existiert. Dank des Vektor-basierten Interrupt-Controllers und dem TCM-bedingten niedrigen Jitter eignet sich die RZ/T1-MPU hervorragend für anspruchsvolle harte Echtzeit-Systeme. Um schnellere Applikationsentwicklung und kürzere Markteinführungszeiten zu erzielen, bietet Renesas das RZ/T1 Drive it! Solution Kit – eine umfassende Hardware/Software-Entwicklungslösung, die bis zu zwei Servomotoren unterstützen kann. Das Kit umfasst eine RZ/T1-CPU-Karte und einen Zweikanal-Niederspannungsumrichter mit Anschlüssen für inkrementelle und absolute Encoder. Der robuste Umrichter verfügt über eine eingebaute Isolation mit Strombegrenzung und Überstromschutz. Ein intelligentes Motion Utility Tool ermittelt Motor-Verdrahtung und -Phasenlage. ge

Kontakt

info

Renesas Electronics Europe GmbH

Düsseldorf

Tel. +49 211 6503-0

SPS IPC Drives: Halle 6, Stand 142

Algorithmen in Quellcode

PLUS

- Stromregelkreis

- Positionsschleife und Feedback

- Positionserfassung

- Space Vector Modulation (SVM)

- Geschwindigkeitsprofil-Generator

- und vieles mehr …

Motion-Control-Bibliothek

- Unterstützung für mehrere Achsen

- Positions-/Drehzahl-Einstellung

- Wicklungs-Mapping

- Kp-, Ki- und Kd-Tuning

- FF Geschwindigkeit/Beschleunigung

- Motor-Kommutationsprofil

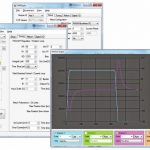

- Echtzeit-Bewegungsdiagramm

- pro Kanal wählbares Zoom-In

Teilen: