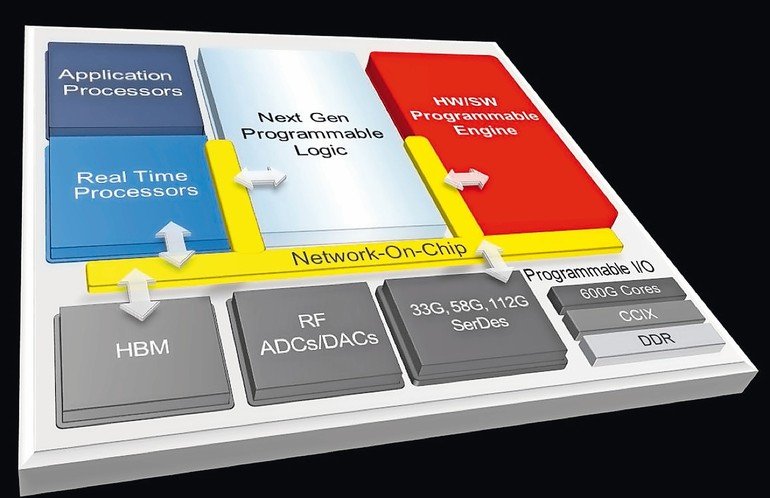

Adaptive Compute Acceleration Platform (ACAP) nennt der Chip-Spezialist Xilinx seine hochintegrierte, heterogene Multi-Core-Rechenplattform, die sich auf der Hardwareebene modifizieren lässt und deren Fähigkeiten über die bisheriger FPGAs hinausgehen soll. Die sogenannte adaptive Rechentechnik soll sich – auch dynamisch während des Betriebs – an die jeweiligen Anforderungen anpassen lassen und eine Leistungsfähigkeit sowie eine auf die Leistungsaufnahme bezogene Performance bieten, wie sie von CPUs oder GPUs nicht erreicht werde, betont Xilinx.

Anwendungen für eine ACAP dürften sich vor allem im wachsenden Big-Data- und KI-Bereich finden. Hierzu gehören das Video-Transcoding, Datenbanken, Datenkompression, Suchen, KI-Inferenzen, die Genomkunde, die maschinelle Bildverarbeitung, Massenspeicher für Computer und die Beschleunigung von Netzwerken. Software- und Hardwareentwickler können zudem ACAP-basierte Produkte für lokale sowie Edge- und Cloud-Anwendungen entwickeln. Die erste ACAP-Produktfamilie mit dem Codenamen ‚Everest‘ wird mit einer 7-nm-Prozesstechnologie von TSMC entwickelt und soll noch in diesem Jahr in die Fertigung gehen. Bereits 2019 soll die Auslieferung an die Kunden beginnen.

Auch Softwareentwickler im Fokus

„Wir haben es hier mit einer grundlegenden technologischen Neuerung für die Industrie und unserer entscheidendsten technischen Errungenschaft seit der Erfindung des FPGA zu tun“, erklärt Victor Peng, President und CEO von Xilinx. „Diese revolutionäre neue Architektur ist außerdem Bestandteil einer groß angelegten Strategie, die dafür sorgen soll, dass Xilinx nicht mehr nur FPGAs anbietet und nur Hardwareentwickler unterstützt.“ Der Einsatz von ACAP in Rechenzentren sowie in darüber hinausgehenden Märkten werde der Nutzung des Adaptive-Computing-Konzepts Auftrieb verleihen und dafür sorgen, dass die intelligente, vernetzte und adaptive Welt schneller Wirklichkeit werde.

Eine ACAP besitzt in ihrem Kern eine FPGA-Struktur neuer Generation mit verteilten Speichern und hardwareprogrammierbaren DSP-Blöcken, einem Multicore-SoC und einer oder mehreren, per Software programmierbaren und zusätzlich hardwaremäßig anpassbaren Rechen-Engines, die über ein Network on Chip (NoC) miteinander verbunden sind. Softwareentwickler können Tools wie C/C++, OpenCL und Python für die Entwicklung ACAP-basierter Systeme nutzen. Mit FPGA-Tools lässt sich eine ACAP außerdem auf der RTL-Ebene programmieren. co

„Wir haben es hier mit einer grundlegenden technologischen Neuerung zu tun.“