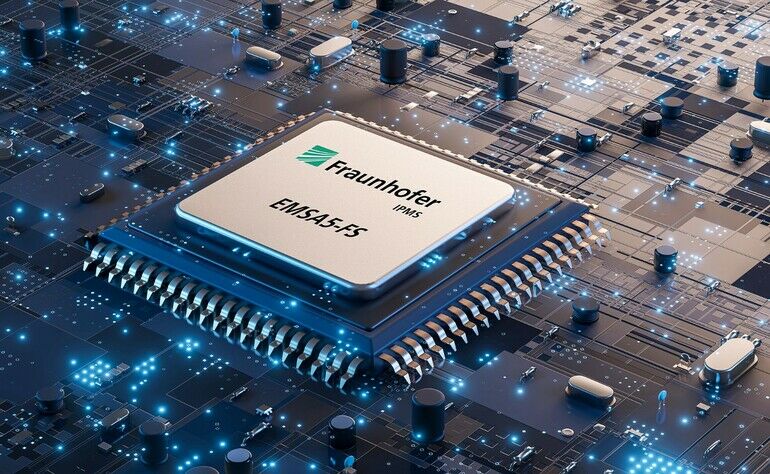

Der vom Fraunhofer IPMS entwickelte Prozessorkern Emsa5-FS für funktionale Sicherheit auf Basis der Open-Source-Befehlssatzarchitektur RISC-V wird durch ein weiteres wichtiges Debugging-Tool unterstützt. Mit der Integration in die Toolsets von Lauterbach stehen nun zahlreiche Debug-Funktionen für den 32-Bit RISC-V Core zur Verfügung.

Der Emsa5-FS ist der erste fehlertolerante Embedded RISC-V-Prozessorkern nach funktionaler Sicherheit. Das Trace32-Toolset von Lauterbach, einem der Weltmarktführer für Hardware-gestützte Debugging-Tools, unterstützt nun auch den Emsa5-FS und bietet Entwicklern umfangreiche Debugging-Funktionen. Der Prozessorkern war der erste RISC-V-Prozessorkern, der als ASIL-D ready nach Automotive Functional Safety zertifiziert wurde und sich damit für den Einsatz in sicherheitskritischen Systemen im Fahrzeug eignet. Er kann sowohl für jede FPGA-Plattform zur Verfügung gestellt als auch in kundenspezifische ASICs für eine breite Palette von Foundry-Technologien integriert werden. Das Fraunhofer IPMS bietet auch Dienstleistungen an, um den IP-Kern mit kundenspezifischen Modulen zu erweitern.

Toolchain-Software unterstützt Fraunhofer IPMS Risc-V-Prozessorkern

Das Trace32-Toolset von Lauterbach bietet Multicore-Debugging auf einzelnen Hardware-Threads von RISC-V-Cores und ermöglicht das Debugging direkt vom Reset-Vektor aus, der für den Test von Startup-Codes und anderen Schlüsselfunktionen benötigt wird. Lauterbach bietet auch High-Level- und Assembler-Debugging für eine Vielzahl von Standard-ISA-Erweiterungen, wie z.B. Compressed Instructions und Floating Points. Darüber hinaus wird das JTAG-Debug-Transportmodul (DTM) vollständig unterstützt. Der Emsa5-FS eignet sich für die Implementierung von Mikrocontrollern in der Automobilindustrie, der Luft- und Raumfahrt, der Medizintechnik und anderen sicherheitskritischen Geräten und Systemen. (eve)